Intel упрощает вход в мир FPGA и ASIC с платформой OFS и eASIC N5X

Программируемые логические интегральные схемы обеспечивают наивысшую гибкость реализации IP-блоков, поскольку из элементов ПЛИС можно создать практически что угодно. Однако они же и гарантируют максимальную сложность разработки. Вполне естественно, что крупные производители ПЛИС стараются снизить порог входа для разработчиков, дабы сделать свою продукцию более популярной. На мероприятии Intel FPGA Day корпорация анонсировала два новых продукта, призванных упростить разработку новых решений на базе ПЛИС, а также перенос уже созданных решений на «фиксированный кремний», чипы ASIC.

Наибольшую гибкость в программном отношении демонстрируют классические центральные процессоры, однако в ряде задач их производительность, как пиковая, так и удельная, оставляет желать лучшего. Менее универсальны и более быстры в этом плане процессоры графические, однако у них есть свои ограничения. Меньше всего ограничений у ПЛИС, однако начать использовать их существенно сложнее, нежели ЦП или ГП.

Помимо построения логической структуры, требуется реализовывать и базовые элементы — работу с памятью и внешними интерфейсами, например, PCI Express или Ethernet. Одной из первых, кто упростил разработчикам эти задачи, стала Xilinx, которая в прошлом году предложила набор стандартных IP-блоков для вышеописанных целей, но по-настоящему модульную FPGA-платформу представила сегодня Intel.

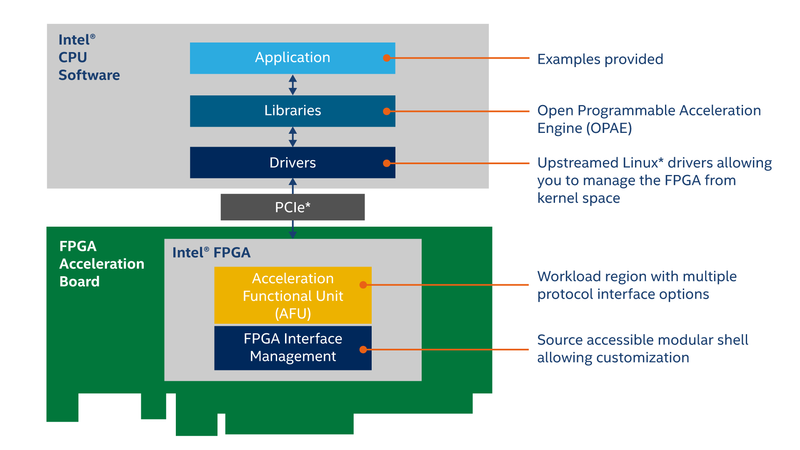

Полное название новой концепции звучит как Intel Open FPGA Stack, сокращённо OFS. Это полноценная программно-аппаратная платформа, позволяющая разработчикам использовать готовые модульные компоненты Intel для реализации базовых возможностей ПЛИС. Можно разрабатывать и собственные IP-модули для работы с памятью или PCIe, но те, кто желает сконцентрироваться на разработке специфических ускорителей и не тратить время и ресурсы на базовые вещи, теперь смогут это сделать благодаря Intel OFS.

В программной части OFS, а именно в самих модулях базовой функциональности, используется открытый код, что благотворно должно сказаться на популярности новой платформы. Более того, имеется поддержка и в основной ветке ядра Linux, что должно ещё более расширить область применения ПЛИС-платформ Intel. Не всегда, однако, сложные и дорогие ПЛИС оптимальны — и тут на сцену выходит вторая анонсированная новинка, Intel eASIC N5X.

ПЛИС обеспечивают максимальную гибкость и позволяют создавать действительно универсальные ускорители, но платить за это приходится как деньгами, так и энергопотреблением. В ряде случаев, когда смена конфигурации ускорителя не требуется, выгоднее обойтись фиксированной реализацией функций в чипах ASIC. И здесь поглощение eASIC, ведущего поставщика структурированных ASIC, которое произошло ещё в 2018 году, начинает приносить свои плоды.

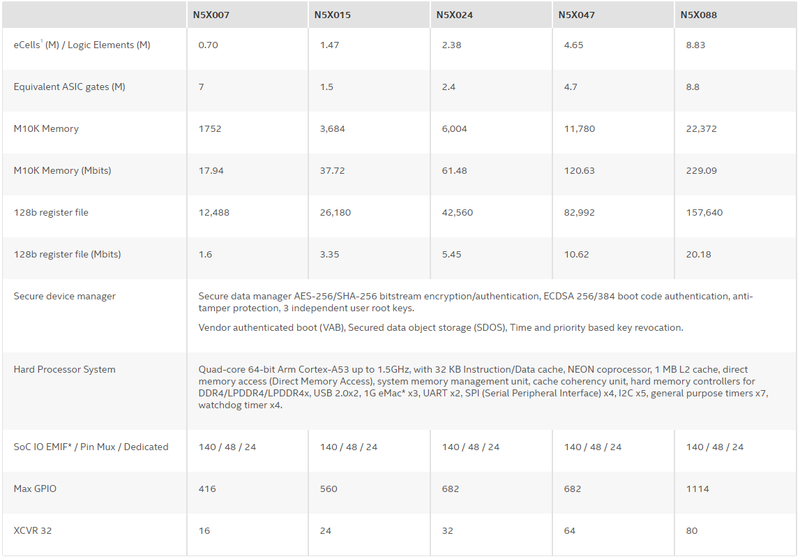

Новые 16-нм чипы серии eASIC N5X представляют собой переходное звено от полноценных ПЛИС к классическим ASIC. Они дешевле и потребляют вдвое меньше энергии, однако позволяют реализовывать достаточно сложные решения: флагманский вариант имеет 8,8 млн. ASIC-эквивалентных структур, 229 Мбит двухпортовой памяти и 20 Мбит для 128-байтных регистровых файлов. Также он может нести до 80 трансиверов 32,44 Гбит/с и имеет четыре фиксированных вычислительных ядра ARMv8.

В eASIC N5X компания-разработчик серьезное внимание уделила вопросам безопасности: в составе чипов имеется аппаратный менеджер, пришедший в новую платформу из семейства ПЛИС Intel Agilex. Он реализует такие функции, как безопасная загрузка, аутентификация и защита от взлома. Таким образом, теперь в распоряжении Intel имеется ещё одна платформа, отлично подходящая для быстрой разработки и развёртывания беспроводных сетей 5G RAN.